在技术创新的推动下,从边缘计算到云的新连接和处理模型也在高速发展,随之而来的,则是对灵活硬件解决方案与日俱增的需求。随着市场上对带宽的要求不断增加,对更快、更灵活的设备的需求也日益迫切。而于近期推出的英特尔Agilex 7 FPGA R-Tile,凭借其高带宽接口和灵活的可编程逻辑,能够满足行业发展需求。目前,基于R-Tile的英特尔Agilex 7 FPGA正在量产。

(相关资料图)

(相关资料图)

近年来,FPGA加速器在市场上的应用率稳步增长,而随着配备R-Tile的FPGA的推出,更高性能的加速器也随之而来。FPGA加速器可以将任务从主机CPU卸载,释放CPU核心并减少总功耗,实现总拥有成本(TCO)的节省。如您作为最终用户、IT专家或云服务提供商,且尚未探索使用FPGA加速器,现在则是一个良好的尝试时机。

●使用FPGA加速器的云服务提供商可以支持更多用户,并释放更多CPU核心给更多的用户,从而获得更多服务收入。

●利用FPGA加速器的原始设备制造商可以节省成本并减少功耗。

英特尔Agilex 7 FPGA产品系列已应需设计以满足市场要求,而且基于R-Tile的版本已经开始量产。

英特尔Agilex 7 FPGA采用了异构多芯片架构,其中位于中心位置的FPGA芯片与收发器芯粒通过英特尔的嵌入式多芯片互连桥接(EMIB)封装技术相连。每个芯粒或区块都是一个小型集成电路芯片,包含一组明确定义的硬化功能子集。这些芯粒使得成本高效的,封装内部高密度互连异构芯片成为现实。通过采用异构多芯片架构和芯粒的设计,英特尔能够在单个设备中提供多样化的功能和灵活性,以满足不同应用的需求。这种方法消除了使用多个设备进行连接的需要,简化了系统设计和集成的复杂性,并提供了更高的可扩展性和性能。

诸多英特尔Agilex 7 FPGA封装组合中都包含了R-Tile芯粒,旨在与高性能CPU连接时可提供行业领先的带宽。R-Tile芯粒结合了PCIe 5.0 x 16和CXL 1.1/2.0的硬化知识产权(IP)块和软件IP代码,为网络、云计算、数据中心、科学计算等诸多领域提供了高度灵活的解决方案。如下是R-Tile支持的关键技术特性列表:

英特尔Agilex 7 FPGA与R-Tile模块的图解

| R-Tile特性(每个区块) | 描述 |

| PCle 5.0 x16Up to32GT/sper lane1x16EP/RP2x8EP/RP4 x4 RP端点(EP)Root Port(RP)PIPE直接事务层旁路/切换选项虚拟化&确切时间选项 | 灵活的、多功能的PCIe 5.0硬化IP模块,允许您在高性能FPGA设计中创建端点、根端口、交换机或定制的PCIe接口。Intel Agilex 7 FPGA R-Tile是唯一具备完整的50x16数据速率且符合PCI-SIG标准的设备。 |

| CXL1.1/2.0x16Up to 32 GT/s per lane1x16 EPSupports CXL Type1 Type2with DCOH and Type 3. | 这是FPGA行业中首款具有CXL硬化IP的设备,可以以全速率管理链接并预处理CXL数据包。软件协议IP管理CXL事务层功能。图形用户界面(GUI)允许进行以下自定义操作:●cxl.io、cxl.cache和cxl.mem接口●允许插入增值加速功能(如定制的压缩/解压缩算法)●创新的主机管理设备内存(HDM)功能与第四代英特尔至强可扩展处理器进行了广泛的验证和互操作性测试。CXL认证待定,将在Compute Express Link协会的活动中进行。预计支持选定的CXL 2.0功能,待验证、互操作性测试和与未来CPU的合格性确认后提供支持。 |

英特尔Agilex 7 FPGA R-Tile关键特性

符合量产要求的R-Tile版本标志着英特尔Agilex 7 FPGA I系列设备中四种不同封装下的七种逻辑密度的器件进入量产阶段。这样一来,客户就能够在他们的新设计中充分利用英特尔Agilex7 FPGA提供的性能和功耗领先优势。基于英特尔10纳米工艺技术,英特尔Agilex 7 FPGA可编程逻辑和R-Tile芯粒充分利用英特尔强大的供应链优势,以及先进的制造和测试能力,能够在标准交货期内提供量产解决方案。一旦英特尔Agilex7 FPGA M系列R-Tile的样品过渡到量产阶段,将具备更多设备密度和封装选项。

将R-Tile的功能与其他的英特尔Agilex 7 FPGA芯粒(如最近发布的F-Tile)相结合,可以创建出适用于下一代加速器(如SmartNIC、IPU和计算存储解决方案)的灵活高性能FPGA。

英特尔(Intel)酷睿 13代 CPU处理器 台式机 原盒 13代 i7-13700KF【16核24线程】

进入购买

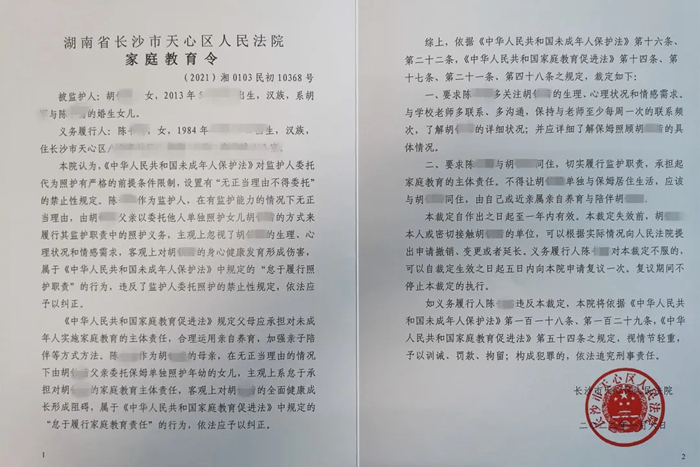

检察官担任法治副校长有了“指挥棒”

检察官担任法治副校长有了“指挥棒” 全国首份《家庭教育令》来了!督促家长“依法带娃”

全国首份《家庭教育令》来了!督促家长“依法带娃” 俄军装甲车辆将具备隐身能力

俄军装甲车辆将具备隐身能力